Contents

What is the Gemini

Spacecraft Computer (OBC)?

The Gemini spacecraft computer

is, as the name implies, the onboard computer of the Gemini

spacecraft. The computer seems to have been referred to

variously as the "spacecraft computer", the "digital computer",

or the "On-Board Computer" (OBC). It was the Gemini

equivalent of Apollo's AGC, though with more limited capabilities

and functionality. Its basic use was in the post-launch

phases of missions (orbit phase, retrograde phase, re-entry

phase), because the Titan II rocket which carried the Gemini

spacecraft into orbit was guided by its own (separate) ACS-15

guidance computer, but there was provision also for switchover to

the Gemini computer for backup guidance if the need arose.

Interestingly, the OBC could be used for automatic attitude

control of the spacecraft, but not automatic velocity control;

rather, it performed necessary calculations for maneuvers such as

orbital insertion or re-entry, and the pilots then performed the

manual chores of actually adjusting the spacecraft velocity

appropriately.

The OBC was designed and manufactured by IBM's Federal Systems

Division, in Owego, New York, just as Apollo's Launch Vehicle Digital Computer (LVDC) was.

The OBC and the LVDC are extraordinarily similar at the CPU

level.

The Gemini VIII OBC, with

cover removed

(Smithsonian National Air & Space Museum)

|

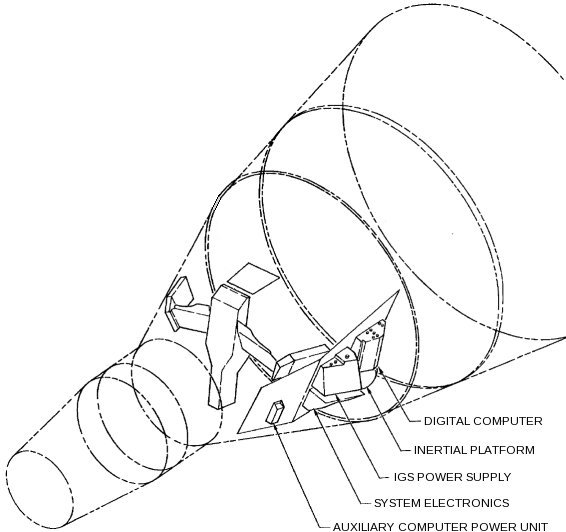

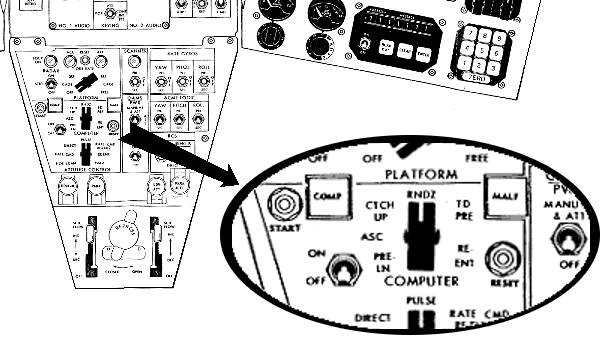

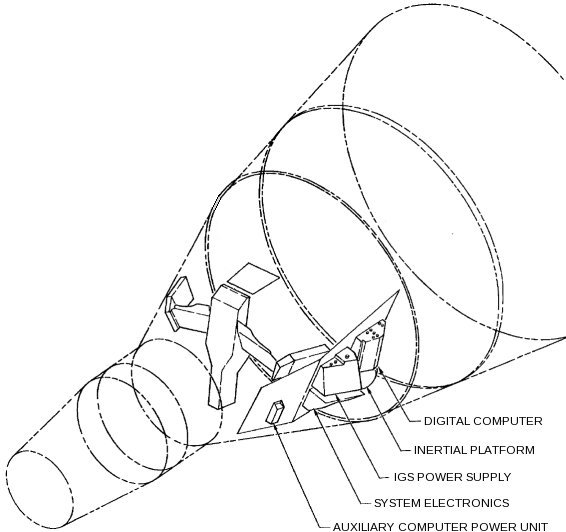

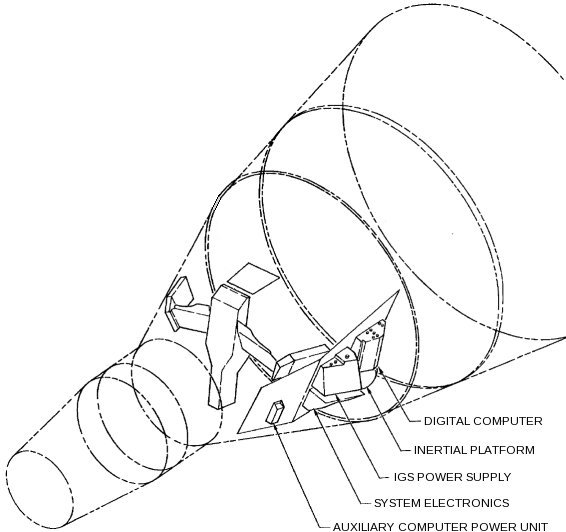

Location of the OBC in the

spacecraft

|

Peripheral Devices

This section

contains a general overview of the OBC's peripheral devices, but

many of them are discussed in much greater detail in later

sections.

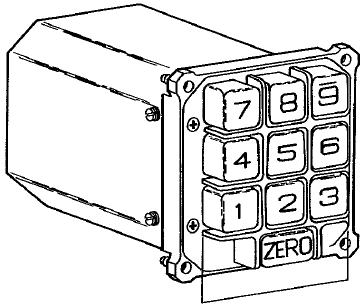

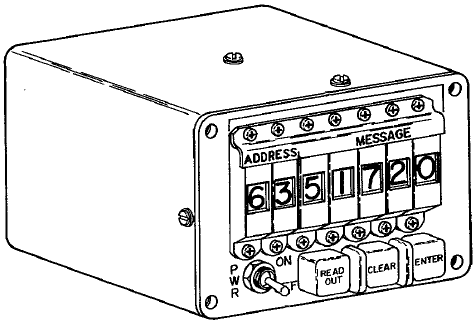

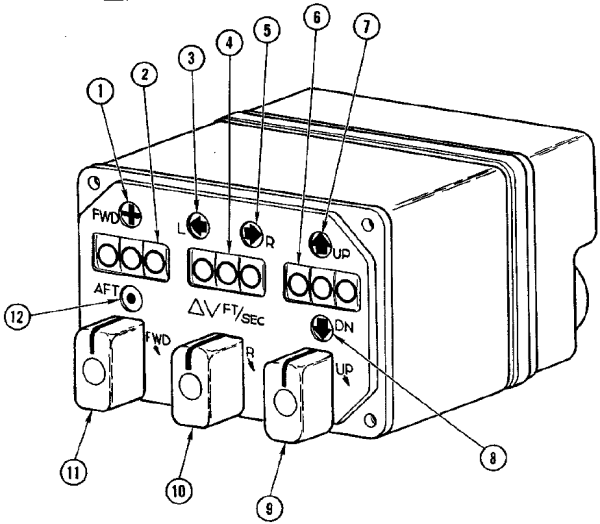

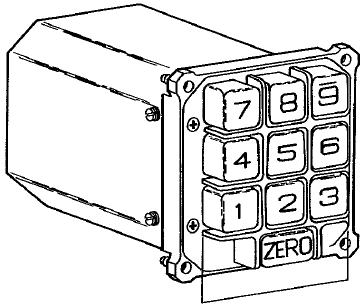

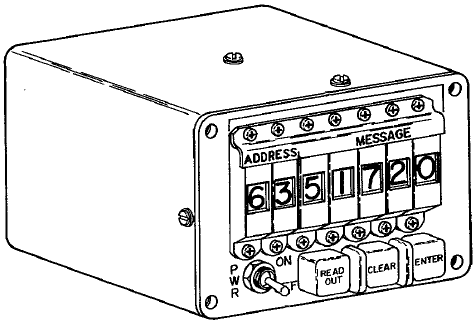

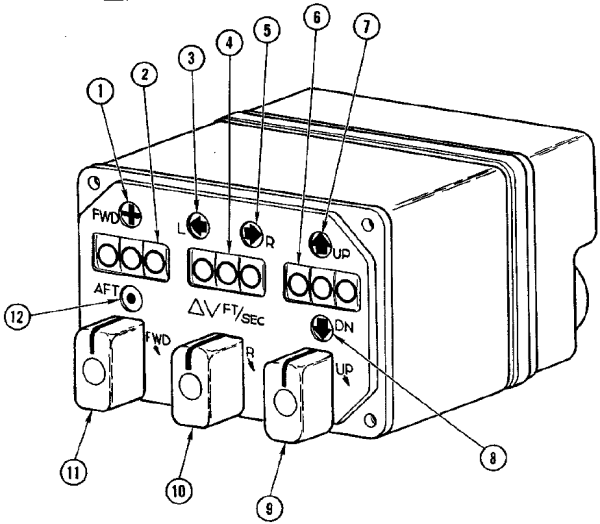

From a user standpoint, the most visible of the OBC's peripheral

device was the Manual Data Insertion Unit (MDIU)—the Gemini

equivalent of the Apollo DSKY—which

comprised the Modular Display Keyboard (MDK) and the Modular

Display Readout (MDR).

Modular Display Keyboard

(MDK)

|

Modular Display

Readout

|

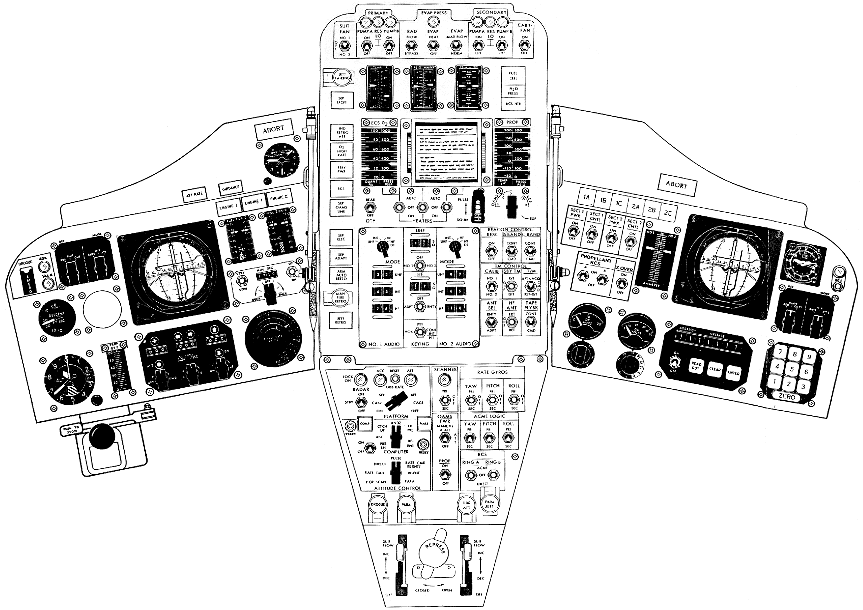

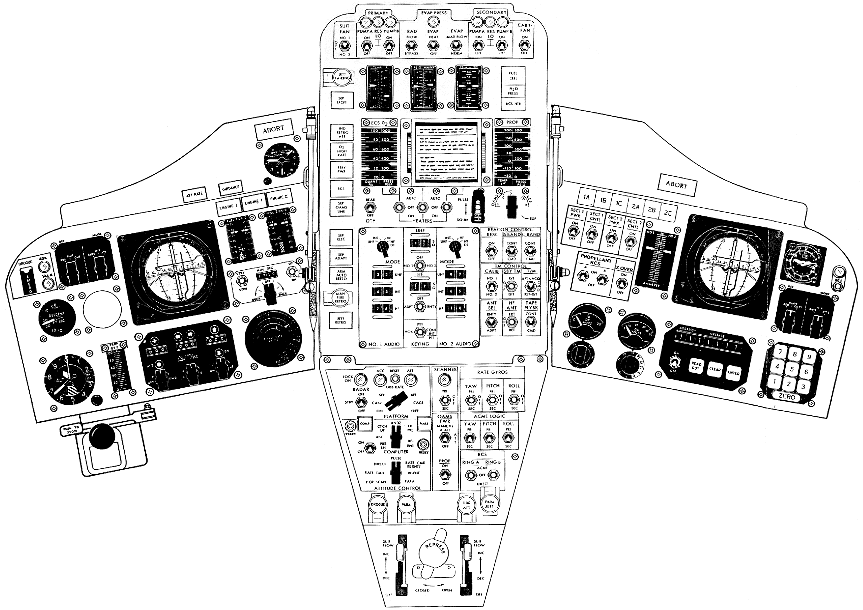

These were on the Pilot's (as opposed to the Command Pilot's)

side of the control panel, at the lower right in the drawing

below. The small image below is from the familiarization

manual, but if you click on it you'll get a much bigger, much

more detailed drawing from the Gemini 5 Mission Report.

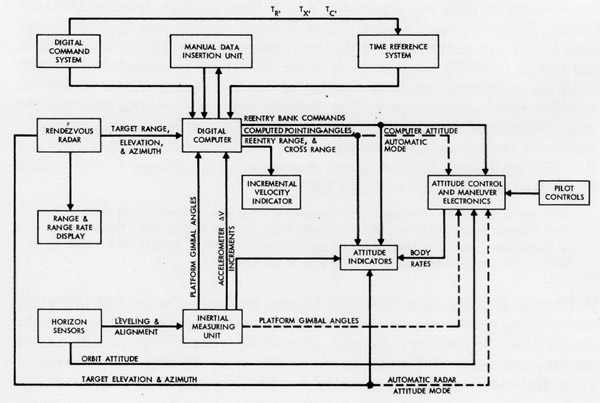

A basic inventory of the guidance sub-systems includes:

- Attitude Control and Maneuver Electronics (ACME), which

is the sub-system that directly controls the propulsion

system.

- Inertial Guidance System (IGS), including the Inertial

Measurement Unit (IMU) and the OBC itself.

- Horizon Sensors

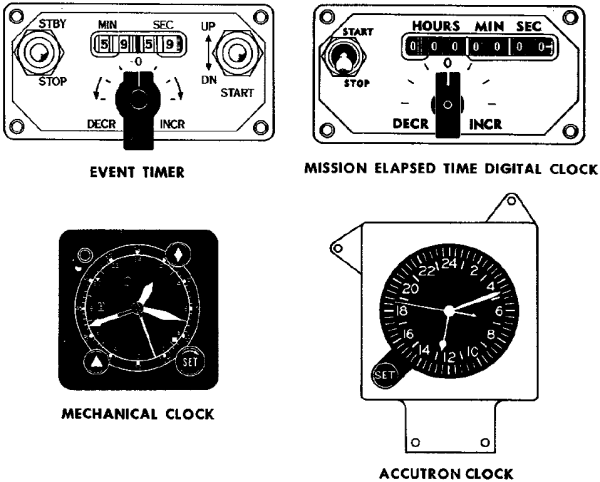

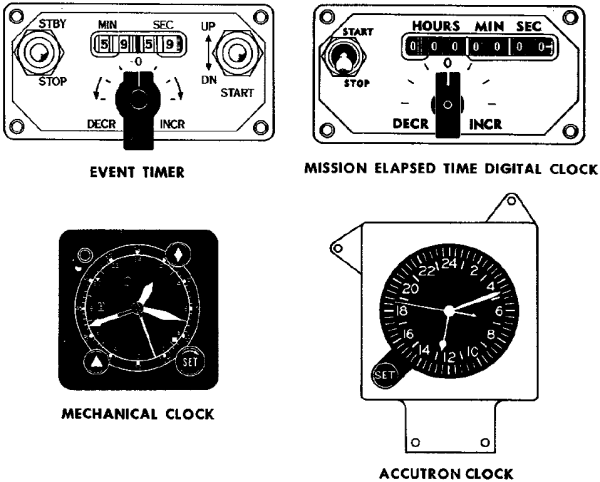

- Time Reference System (TRS)

The diagram below shows a very simplified block diagram

of the guidance system, but if you click it you'll get a

(different) more-detailed block diagram.

The IMU is the usual gimballed stable platform with

accelerometers and angular resolvers as in Apollo, except for

a key difference that the Gemini IMU had four gimbals rather

than the three gimbals of Apollo. This means that it

was not subject to the phenomenon of "gimbal lock", and hence

the software used to adjust spacecraft alignment could be

simpler than with three gimbals. The value of the 4th

gimbal can be appreciated when considering incidents like the

mishap in Gemini VIII in which an uncontrolled roll

occurred. (If the IMU had had only three gimbals, my

understanding is that gimbal lock would have occured when the

roll angle was too great.) On the other hand, at that

point the spacecraft was under manual control anyway, and I'm

sure that the notion that the IMU would have to be realigned

later would have been the least of Neil Armstrong and Dave

Scott's worries.

Gemini Documentation

Sadly,

documentation we've been able to collect for the OBC lags far

behind that of the AGC or even that of the Abort Guidance System

(AGS). What little survives that we have been able to

access can be found in our Document

Library. There's a lot of unique stuff there

contributed by original Gemini developers.

Evolution of the Flight

Software ... or, "Everybody Loves Math Flow 7" ... or, "What is

software, my man? What is software?"

Information

about the Gemini OBC software is hard to come by. Useful

information we don't

have includes any actual OBC software that's contemporary to the

Gemini project itself, and that's a lot not to know. But

the situation isn't all bad, partly because the development

method of the Gemini OBC software causes us to question what the

notion of having the original software even means. I'll

explain more about that shortly, but there's an important sense

in which we actually do have significant portions of the software

at our disposal.

But before turning our attention to such lofty matters, let's

begin with some of the more-mundane details. Firstly, as

far as naming is concerned, the flight software seems to have

been called simply the "operational program". On the

subject of versioning of the operational program, we have only

partial information, from the familiarization manual, from

James

Tomayko's Computers in Spaceflight, Chapter 1, section 4, and

from

this short memo. (Where there's any discrepancy, I

personally believe in the memo.)

The operational programs were characterized in terms of something

called the "Math Flow". In brief, the Math Flow is the

complete design of the software, expressed in Gemini as a series

of very detailed flowcharts. The development of the Math

Flow eventualy went through 7 major versions, designated MF-1

through MF-7. But there were differing revisions for each

of the major versions as well.

The overall software design was partitioned into several

different areas of basic functionality. In math-flow MF-1 through

MF-6, these functional areas were integrated into a single

operational program. (Though for some missions, unneeded

functionality could be omitted. Thus, Catch-up & Rendezvous

were omitted in spacecraft GT-3, GT-4, and GT-7.) In MF-7,

the code was refactored into 6 different high-level "Program

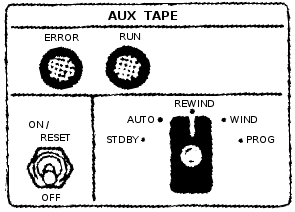

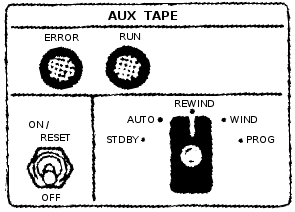

Modules", which could be loaded into memory from the Auxiliary Tape Memory

(ATM) when needed during specific mission phases, though

Module I was in memory at all times and didn't need to be loaded

from the ATM. The modules were as follows:

Module

| Basic

Functionality

|

|---|

MOD I

| Executor

Pre-Launch

Diagnostics

Computational subroutines (SINCOS, SQROOT, etc.)

ATM-read

|

MOD II

| Ascent (with abort

capability)

Catch-up (without radar)

Re-entry for ascent-abort

|

MOD III

| Catch-up (with radar)

Rendezvous

|

MOD IV

| Touchdown-predict

Re-entry

Re-entry initialization

|

MOD V

|

Simplified functions as backup for ATM failure:

Ascent (without abort capability)

Catch-up and Rendezvous (without self-test)

|

MOD VI

| Orbit-predict

Orbit-navigation

Orbit-determination

|

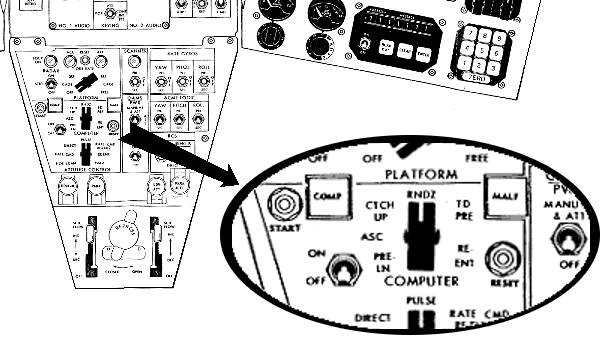

The astronauts used the Computer Mode rotary switch on the

Pilots' Control and Display Panel to select

from amount the following mission phases to indirectly affect the

active functionality areas: Pre-launch, Ascent, Catch-up,

Rendezvous, or Re-entry.

All of these functionality areas are self-explanatory, except

"Executor". Executor is the interface that interrelates the

other software modules and allows them to interact with each

other, as well has implementing certain common functionality

among them.

As far as the relationship between this stuff and the missions is

concerned, the best info I have at present is as follows:

Spacecraft

|

Mission

Designation

|

Math Flow

version

|

Program

number,

revision

|

Comments

|

|---|

GT-1

| Gemini 1

| n/a

| n/a

| Unmanned mission.

Since Gemini I was apparently intended principally as a

structural test of the spacecraft, it may not have had a

computer onboard.

|

n/a

| n/a

| MF-1

| -

|

|

n/a

| n/a

| MF-2

| -

|

|

n/a

|

n/a

|

MF-3

|

6444540, B |

Flowcharts that we have! Seemingly, one minor

revision prior to the software flown in the Gemini 2

unmanned mission. You'll notice, though, that the

first manned missions (Gemini 3 and 4) still used MF-3,

though in a later minor revision. It's useful to

know that:

- Rendezvous begins on p. 1

- Gimbal Angle and CLOCK subroutines are on p. 8

- SINCOS and ARCTAN subroutines are on p. 9

- Re-entry begins on p. 10

- SHIFT, SQRT (also computes arcsin), and LOG

subroutines are on p. 15

- MDIU subroutine is on p. 16

- Ascent guidance begins on p. 17

- Fast-loop ascent guidance begins on p. 19

- Root sum subroutine begins on p. 22

- Executor, Accelerometer, DCS, and DAS are on p.

23

- MDIU scaling stuff starts on p. 24

- AGE is on p. 26

- Standby, TRS, and I/O subroutines are on p.

27

|

n/a

|

n/a

|

MF-3(?)

|

62-564-0020, B

(Ascent Guidance and

Fast Ascent Guidance only)

|

Flowcharts that we have! See pp. 2-3 of the linked

document. The document contains a lot of other

helpful stuff like detailed explanations of the variables,

some additional theory, and source code of a FORTRAN

implementation.

I'm not really clear where this goes in the development

chronology, merely that it is a few months later than the

corresponding elements from the Detailed Math Flow in the

preceding entry.

|

GT-2

| Gemini 2

| MF-3

|

6444541, C | Unmanned

mission.

|

GT-3

| Gemini III

| MF-3

| 6444566, C | First manned

mission.

|

GT-4

| Gemini IV

| MF-3

| 6444909, C

|

|

n/a

| n/a

| MF-4

| -

| Work stopped prior to

"sell off".

|

n/a

| n/a

| MF-5

| -

| Work stopped prior to

release or sell off.

|

GT-5

| Gemini V

| MF-6

| 6444871, B

|

|

GT-6

| Gemini VI-A

| MF-6

|

6444871, D

|

|

GT-7

| Gemini VII

| MF-6

| 6444871, D |

|

GT-8 (backup)

| n/a

| MF-6

| 6444871, E

|

|

GT-8

| Gemini VIII

| MF-7

| MOD I:

6449856, C

MOD II: not used

MOD III: not used

MOD IV: 6449864, B

MOD V: 6449812, B

MOD VI: not used

| The principal

difference between MF-6 and MF-7 was the reworking of the

integrated operational program into 6 individual Modules

(here referred to as MOD I through MOD VI) that were

treated as independent programs, loadable into main memory

at runtime from the new Auxiliary Tape Memory (ATM).

One consequence is that each of the 6 Modules in MF-7 now

had its own individual program number and

revision.

|

GT-9

| Gemini IX-A

| MF-7

| MOD I: 6449856, C

MOD II: not used

MOD III: not used

MOD IV: 6449864, B

MOD V: 6449812, B

MOD VI: not used |

|

n/a

|

n/a

|

MF-7

|

MOD III: 6449883 |

Flowcharts that we have! Later than any Module III

flown prior to the ATM, and therefore presumably

algorithmically mature, but preceding (by some unknown

number of revisions) the first use of Module III as an

integrated program loaded from the ATM in Gemini X and

therefore presumably relatively immature in terms of its

implementation in OBC assembly language. But

remember, we don't have any of the original OBC assembly

language, and it's only the algorithmic correctness that

concerns us.

Incidentally, this scan derived from a microfilm retrieved

from a wastebasket prior to the project's move from the

Washington, D.C., area in mid-1966. Obviously, we're

always trying to find better sources of material. (If

you happen to have any wastebaskets from that era that are

still loaded with microfilm, be sure to let us know.) |

GT-10

| Gemini X | MF-7

| MOD I:

6449856, C (?)

MOD II: 6449816, A

MOD III: 6449895

MOD IV: 6449864, B (?)

MOD V: 6449812, B (?)

MOD VI: 6450027

|

|

GT-11

| Gemini XI

| MF-7

| ?

|

|

GT-12

| Gemini XII

| MF-7

| ?

|

|

Finally, let's return to odd question of whether or not we're in

possession of any of the original flight software. This

question is related to the serious if somewhat

facetiously-phrased question asked in this title's heading,

namely: "What is software?" In the context of the

Virtual AGC project --- and I think in the minds of most

currently-active computer programmers (2011) --- the question

"What is software?" is very easily answered: If you have

the source code of the program (and some way of compiling or

assembling that code) or if you have the binary executable of the

program (and some way to execute it), then you have the

software. If you have all of the instructions for how to

compile/assemble it, so much the better. But the OBC

software developers had a somewhat different view of this

question, and their view is bound up in the method used to

develop the software.

The most important thing to understand about the

software-development process for the OBC software is that it was

very heavily dependent on design as opposed to coding. What

I mean by that is the following:

- Great attention was given to deriving the mathematics

needed for achieving the objectives, and great attention was

given as well to verifying the correctness of that

mathematics.

- Then (and only then), great attention was given to

developing the "Math Flow". To repeat what I said

earlier, the Math Flow was a series of a flowcharts specifying

the algorithms to be implemented in very great detail.

The flowcharts described the algorithms in such detail that the

programmer had very few options left open to him in actually

coding that software into a form that could be compiled or

assembled.

- Then (and only then), software was coded. But the

coding was almost entirely a slavish detail-by-detail

translation of the flowchart into computer source-code

form.

It was interesting (and at first frustrating) for me to

discuss the matter of existence of the software with OBC

developers, because from my point of view the software (source

code) seemingly no longer existed, while from the point of view

of the OBC developers the software did still exist to the extent

that the flowcharts still existed ... because to them the

software is the

flowchart and not the source code. The source code could

always be reproduced from the flowchart, albeit with great

effort, and not necessarily byte-for-byte identical to the

original. When viewed from this perspective, it makes

little difference how the flowchart is translated into computer

language—whether into FORTRAN as was done for simulation purposes

or into OBC assembly language for the mission computer—because

regardless, it's the same flowchart so it's the same program.

Now, in the preceding paragraph I probably exaggerated the OBC

developers' somewhat in order to make my point, but I think there

is nevertheless a lot of validity in the viewpoint that was

expressed: If we have the Math Flow charts, then we have

the software. You'll notice from the table above that we do

have some of the Math Flow charts, though the validity of what we

have could be debated.

I'll leave it as an exercise for the reader to decide whether or

not we actually have any of the software, or whether or not we're

rationalizing.

OBC Architecture and

Interfacing

References

The

principal known sources of information about the computer itself

are the "Guidance and Control" sections (Section VIII) of the

Project Gemini Familiarization

Manual,

Volume 1 and

Volume 2, and most of the information on this web-page was

extracted from those sources. If you find my redigesting of

the material too poor, you may want to read the Manual

instead. However, any simulation software, assemblers,

etc., will be based on my understanding and hence on the

content of this web-page, so please bring any errors to my

attention.

Also, I should state that there's a lot of information on this

page that comes from personal communications with original OBC

developers, and can't be found in any other reference that's

going to be available to the reader ... or probably, to

anyone. While I present a general acknowledgements and

"homage" to the original OBC developers in general at the very

end of this web-page, let me mention here the OBC developers who

have been so directly helpful to me. In no particular

order:

- Gene Mertz

- Charlie Leist

- Alden Minnick

- Don O'Neill

General

Characteristics of the OBC

The OBC measured

18.9"(H)×14.5"(W)×12.75"(D), and weighed 58.98 pounds. OBC

power was supplied by the IGS Power Supply, which was itself

powered from the spacecraft's main +28VDC bus or (for very brief

main-power outages or brownouts) the Auxiliary Computer Power

Unit (ACPU). The OBC required various voltages (+27.2VDC,

+9.3VDC -27.2VDC, +20VDC, +28VDC, and 26VAC, but the existing

documentation is inconsistent on the exact voltages used), and

itself supplied the MDIU (+25VDC, -25VDC +8VDC) and these latter

three voltages were what was actually used internally by the OBC

itself.

The computing characteristics were:

- 39 bits per memory word. Each memory word comprised

three "syllables" (syllable 0, syllable 1, and syllable 2) of

13 bits each.

- 4096 words of memory, in a ferrite core array. All of

this RAM was writable—i.e., there was no read-only memory—but

the readout of the memory was non-destructive.

- The memory was logically divided into 16 "sectors" of 256

words each.

- At any given time only 2 sectors are actually accessable,

the current sector (selectable under program control) and the

"residual" sector (sector 17 octal).

- The third syllables of memory words were writable by the

OBC hardware, but this function was disabled after the

spacecraft left the hangar, so at that point the 3rd syllables

were effectively read-only. Consequently, data words

always needed to be placed into the first two syllables of

memory words. The addressing of data by CPU instructions

enforced this data alignment anyway.

- "Instruction words" were 13 bits each, and "data words"

were 26 bits each, so any given memory word could have had a

data word and/or several instruction words packed into

it. There were also provisions for "short" data words of

13 bits, but these short data words could be used only for

testing purposes by Aerospace Ground

Equipment (AGE), and so were irrelevant for software.

- Integer arithmetic was 2's-complement.

- Instruction cycle time was 140 μs and all instructions

required a single cycle except for MLT and DIV.

Layout of Memory Words

I should

make it clear that in this section I'm describing my perspective

on the organization of OBC memory, in terms of how the original

OBC programmers would have worked with it, in terms of how one

would work with it using the tools I've created for this site,

and in terms of what I think would be the thinking of "modern"

programmers at the time I'm writing these words (2011). I'm

not slavishly reproducing here the material on memory

orgainization from the most-complete documentation available to

us, namely the "Guidance and Control" sections (Section VIII) of

the Project Gemini

Familiarization Manual,

Volume 1 and

Volume 2, because that documentation seems to me to conflict

with what I"ve been told by actual OBC programmers. The

specific area of difficulty is bit-ordering within memory

words. You see, the memory was accessed by a kind of serial

interface, and the natural hardware view is in terms of the

time-order in which the bits are shifted in and out ... whereas

the natural software or mathematical view is in terms of which

bits are the most-significant or least-significant—or as normally

represented, which bits are on the "left" and which are on the

"right". So I'll adopt the latter perspective, but if you

wish to explore what the documentation says on the topic of

bit-ordering, feel free to do so.

In all cases, when I show you binary or octal representations of

OBC memory, it will use the notation common today, in which the

least-significant bits or octal digits are on the right and the

most-significant bits or octal digits are on the left.

As mentioned earlier, memory words are 39 bits, comprising three

13-bit "syllables". In most ways, the syllable is really

the natural memory unit, and not the word. Except in one

specific case, storing and retrieving 26-bit data, syllables

within a memory word are completely unrelated to (and independent

of) each other. So you're really best served by thinking of

memory as a set of syllables rather than a set of words.

Not all syllables are created equal. In the normal

operating mode of the OBC at mission time, the following rules

apply:

- All CPU instructions which fetch, store, or otherwise

operate on data stored in memory work only with 26-bit (2-syllable) data

words in which the less-significant syllable is stored in

syllable 0 of memory and the more-significant word is stored in

syllable 1 (in the same word) of memory.

- Only syllables 0 and 1 are cabable of being modified.

Syllable 2 is read-only.

- Therefore, as you can imagine, all data other than code is

allocated in syllables 0 and 1.

- Code is commonly stored in syllable 2 ... though since data

does not use all of syllables 0 and 1, some code will be stored

in syllables 0 and 1 as well.

(There's also a less-common operating mode called "half-word

mode" which has somewhat different rules, but this mode has

limited usage so we'll return to it later rather than diverting

the main discussion.)

Now let's look at some common syllable or double-syllable

formats.

Every CPU instruction consists of a single syllable, in the

following bit layout:

PPPPAAAAAAAAA

where PPPP is a

4-bit code identifying the specific CPU instruction (the "op

code") and AAAAAAAAA is

a 9-bit code (3 octal digits) identifying (in a way that varies

by instruction type) the operand for the instruction.

Conventionally, OBC programmers name the individual bits like

so:

- OP4 is the

most-significant bit of PPPP and

OP1 is the

least-significant.

- A9 is the

most-significant bit of AAAAAAAAA

and A1 is the

least-significant.

In most instruction types, A1-A8 select

a particular memory word. Since there are only 8 bits, only

256 different words are accessible. Recall, moreover, that

memory consists of 16 sectors of 256 words each of 3 syllables

each. So the instruction is able to select a specific word

address, but the sector containing the word and the syllable

within the word can't be selected ... those have to be known by

other means, which we'll discuss later; for now, just realize

that at any time there's some "current sector" and "current

syllable", and that whatever the CPU is doing operates within

that current selection. When A1-A8 is

interpreted in this way, A9 can be

used to override the current sector and instead to do a one-time

selection of sector 0, which is referred to as the "residual

sector". A9=0 means

to use the current sector and A9=1 means

to use the residual sector. But there's no way to select a

different sector or a different syllable on an

individual-instruction basis.

Several instructions use a scheme in which the field consisting

of bits A1-A3 is

given the name "X" and A4-A6 are

given the name "Y", thus giving the instruction two independent

parameters. In those cases, A7 and

A8 are

unused, and A9 may or

may supply additional functionality

For normal 26-bit data, recall that a standard 2's-complement

format is used. OBC programmers conventionally refer to the

sign bit (i.e., the most-significant bit if interpreting the data

as an unsigned integer) as S, to the

most-significant non-sign bit as M25, and to

the least-significant bit as M1.

Therefore, in a word containing such data, syllable 1 will

contain S and

M25-M14;

syllable 0 will contain M13-M1.

Numerical data can be interpreted in two different ways,

depending on the interpretation of the software. Obviously,

the data could be interpreted as a simple 2's complement

integer. It can also be interpreted as a fractional value

with absolute value less than 1.0. In the latter

interpretation, there is some scaling factor needed to relate the

actual value of the number to the binary value that's stored in

memory. The OBC and its software have no method for dealing with

scaling factors, and it was up to the programmer to understand

which interpretation was used, as well as to explicitly scale

values during computations to avoid overflow and loss of

significant bits.

An important variation in which 26 bits of data aren't numerical

in nature is the so-called "HOP constant". A "HOP constant"

is used by a dedicated CPU instruction (HOP)

to change things such as the currently-selected memory sector and

syllable by loading a hidden CPU register that can't be accessed

by other means. The layout of a HOP constant is as follows:

xxxxxxxxHxSSxPPPPAAAAAAAAA

In this scheme:

- Bits AAAAAAAAA

are given names A9-A1 and

are interpreted as described earlier, in that they allow

selection of a word address (0-255) and provide an override for

current-sector vs. residual sector. After the

HOP

instruction executes, this setting persists within the CPU's

hidden HOP register only for the current instruction and is

then incremented to the next sequential word (or to some other

word if a branch occurs).

- Bits SS,

respectively given the names SYB and

SYA,

specify the current syllable: 00 for syllable 0, 01 for

syllable 1, and 10 for syllable 2. After the HOP

instruction executes, this setting persists until another

HOP

instruction changes it.

- Bits PPPP,

respectively given the names S4-S1,

specify the current sector. After the HOP

instruction executes, this setting persists until another

HOP

instruction changes it, though as we've seen it can be

overridden to instead use sector 0 on an

instruction-by-instruction basis using the A9 feature

possessed by some of the CPU instructions.

- H selects

between "normal" mode (H=0) and

"half-word" mode (H=1), and

this mode persists until another HOP

instruction changes it. "Normal" mode is what I've been

describing to you up to this point. In half-word mode

(HWM), the data comes from syllable 2 rather than

syllables 0,1, and therefore is only 13 bits rather than

26. When the CPU fetches such data from memory, it fills

the least-significant 13 bits of the CPU's accumulator

register, while the most-significant 13-bits are all 0.

An interesting consequence of being in the half-word mode is

that any HOP

instruction will return to normal mode (since H is among

the higher 13 bits of a HOP constant) and the current syllable

will always become 0 (since SYB and

SYA are

also among the 13 more-signficant bits). Moreover, since

the the OBC's ability to write to syllable 2 is disabled after

the spacecraft has left the hangar, no STO or

SPQ have

any effect in half-word mode.

- At power-up, the behavior differed between the early Gemini

missions without ATM (Auxiliary Tape Memory), and the later

ones with ATM:

- Without ATM, it is as if a HOP constant is loaded that

puts the unit in normal mode (i.e., not half-word mode) at

syllable 0 of word 0 in sector 0.

- With ATM, it is as if a HOP constant is loaded that puts

the unit into half-word mode at syllable 2 of word 0 in

sector 0.

You may wonder what half-word mode is good for? Well,

originally, it seems to have been intended for testing

purposes. Later, when the flight-program outstripped the

size of available memory, it became necessary to add the ATM and

use it to overlay programs at runtime. In that case, I

guess, it's useful to be able to run a program entirely within

syllable 2 (which is read-only) without fear that the ATM can

overlay it. But you know, I'm not really sure.

Instruction Sequencing

You may

na\EFvely suppose (I did!) if you did not read the preceding

section in great detail, that the everyday usage of the words

"word" and "syllable" applies similarly in stepping through the

OBC (or LVDC) instructions. In proceeding through a

sentence of natural language like English, you use up all of the

syllables in a word before proceeding to the next word. So

you might suppose that OBC instructions would sequence in a

manner something like the following: word N

syllable 0, word N

syllable 1, word N

syllable 2, word N+1

syllable 0, word N+1

syllable 1, and so on. In fact, this is not the case at

all, and (as you may infer from the instruction definitions in

the following section) would have caused insuperable

difficulties. So get the na\EFve interpretation right out

of your head!

Instead, the instruction

sequencing was like this:

word 0 syllable N

word 1 syllable N

word 2 syllable N

etc.

so that the syllable number never changed automatically as you

progressed through the program. But you could always change

the syllable manually by executing an instruction

(HOP)

and a HOP constant specifically designed to change the syllable

number.

In retrospect, from an outsiders point of view, it would perhaps

have been less confusing in terms of instruction sequencing if

the OBC hardware designers had used the word "paragraph" rather

than "syllable". Alas! it's a bit late to worry about that

now. The OBC programmers I've consulted seem to think that

this is a perfectly natural scheme, and don't seem to have

experienced any confusion over the concept of

"syllables".

CPU

Instructions

If you're interested in Gemini, you may not be

very interested in Apollo's LVDC instruction set. But

there are so many similarities between the two that I'll probably

not be able to resist the temptation to point out some of the

differences as I proceed. A difference not pointed out in

the table below is that the LVDC instructions MPH,

XOR, and

CDS,

EXM are not

present in the OBC.

Note that in what follows, a name representing a location of

memory holding an instruction is called a "left-hand symbol" in

the parliance of the Gemini OBC programmers, and I will continue

to call it that (or LHS for short) rather than adopting

more-current terminology.

Finally, when I talk below about the assembly-language syntax of

the instructions, I'm referring to the syntax supported by my own

yaASM assembler presented

as a download on this website. This syntax is very similar

to the original OBC assembler's syntax but we can't be sure it's

identical because no documentation for the original assembler has

been located up to this point in time.

Mnemonic

| Opcode

(OP1-OP4)

in octal

|

Timing

(140 μs

cycles)

|

Description of the instruction

|

|---|

HOP

|

00

|

1

|

This instruction combines an unconditional jump

instruction with various other configuration options,

such as memory-sector selection. The way it works

is that the address A1-A9 points to a memory word that

contains a "HOP constant", and the HOP

instruction transfers that HOP constant into the HOP

register. Recall that A1-A8 select the offset

within a 256-word sector, and A9 is the "residual bit"

that selects between the current sector and the "residual

sector". There is no provision for a partial HOP

constant, and the full HOP constant needs to be given

every time a HOP

instruction is used. See also TRA.

However ... the fact that HOP

operates on HOP constants rather than on the left-hand

symbols that are the labels for locations in the code as

actually understood by the programmers, is not very

convenient. The simple act of HOPping to a location

would have to look something like this:

HTARGET

HOPC TARGET # Set

up a HOP constant for the target location.

...

HOP HTARGET # HOP

to the target location

...

TARGET

...

# Location we want to HOP to.

This is pretty cumbersome. The assembler therefore

provides a special feature in that if the operand of a

HOP is a left-hand symbol for a code location, which

would otherwise be illegal, the assembler silently

allocates and initializes a HOP constant of the same

name, but enclosed in parentheses, and then it pretends

that the operand of the HOP was really the newly-created

HOP constant. Therefore, in assembly language, the

following becomes legal even though seemingly illegal in

machine code:

HOP TARGET #

HOP to the target location

...

TARGET

...

# Location we want to HOP to.

But what the assembler really outputs in this case is the

same as in the first example (with the HOP constant named

"(TARGET)"

instead of "HTARGET").

The assembler performs a similar service for the

CLA

and STO

instructions (see below). There are some drawbacks to

this special feature as well, namely:

- Any left-hand symbols used as targets of HOPs in

this way must be 6 characters or less rather than

8.

- The assembler always creates the implicit HOP

constants in the residual sector 17, syllable 0.

- Since there are no explicit allocations for the

implicit HOP constants, it's easy for the programmer to

overlook that they're being created, and therefore to

be less aware of the rate at which memory is being used

up.

- There's no provision for half-word mode.

Fortunately, there's no drawback here that can't be

worked around by explicitly defining any troublesome HOP

constants needed, as in the first example.

|

DIV

|

01

|

1

(results

available

after 6)

|

This is the division instruction. The contents of

the accumulator are divided by the operand pointed to by

the address A1-A9 embedded within the instruction to

produce a 24-bit quotient. Recall that A1-A8 select

the offset within a 256-word sector, and A9 is the

"residual bit" that selects between the current sector

and the "residual sector". The quotient is

available via the SPQ

instruction from the 5th instruction following the

DIV.

In other words, 4 other instructions not involving

multiplication or division can be performed in the

interval between DIV

and SPQ.

To illustrate the assembly-language syntax, let's divide

the integer 56 by 3 and store the result in a

variable:

RESULT

# Allocate variable for output.

K56

DEC

56 # Provide

dividend as a constant.

K3

DEC

3 #

Provide divisor as a constant.

CLA

K56 # Load divisor

into accumulator.

DIV

K3 # Start

the division.

NOP

# The result won't be available

NOP

# for a while, so kill some time.

NOP

NOP

SPQ

# Fetch quotient into accumulator.

STO RESULT #

Save it!

|

PRO

|

02

|

1

|

Inputs or outputs an i/o "signal" into or from the

accumulator. (In the AGC these are called

"channels". In current terminology, we'd probably

usually refer to them as "ports".) Whether or not

an input or an output is performed depends on the

particular signal chosen. The X (A1-A3) and Y

(A4-A6) operand fields are used for signal

selection. A9 is used as well. For an output

operation, it determines if the accumulator should be

cleared after the output (A9=1) or preserved

(A9=0). For an input operation, it determines

if the data should be loaded into the accumulator (A9=1)

or logically OR'd with the accumulator (A9=0). A

table of the i/o signals vs. addresses is given in the

following

section. (The PRO

instruction is essentially equivalent to the LVDC PIO

instruction, but the selection of i/o signals is

different.)

The documentation does not explain this, but I think that

when the PRO

instruction is accessing a single-bit signal, only the

accumulator's sign bit is used as the output or the

input. (I'm not sure what the effect on other

bit-positions should be on input.)

There are several allowable assembly-language syntaxes

for this instruction:

PRO

YX # If

A9=0

PRO

0YX # Same as

"PRO YX"

PRO

4YX # If

A9=1

(Or, you could just look at it as having a literal

octal constant as operand, and that constant was placed

directly into the bits A9-A1.) For example, to read

MDIU keystroke data, X=3 and Y=4, so

PRO

43

|

RSU

|

03

|

1

|

Same as SUB

(see below), except that the order of the operands in the

subtraction is reversed.

Assembly-language example to compute RESULT=3-56:

RESULT

# Allocate variable for output.

ARG1

DEC 56

ARG2 DEC

3

CLA ARG1

RSU

ARG2

STO RESULT |

ADD

|

04

|

1

|

Adds the contents of the accumulator with the contents of

the address embedded within the instruction and places

the result in the accumulator. Recall that A1-A8

select the offset within a 256-word sector, and A9 is the

"residual bit" that selects between the current sector

and the "residual sector".

Assembly-language example to compute RESULT=56+3:

RESULT

# Allocate variable for output.

ARG1

DEC 56

ARG2 DEC

3

CLA ARG1

ADD

ARG2

STO

RESULT

|

SUB

|

05

|

1

|

Subtracts the contents of a word pointed to by the

address embedded within the instruction from the

accumulator, and puts the result back into the

accumulator. Recall that A1-A8 select the offset

within a 256-word sector, and A9 is the "residual bit"

that selects between the current sector and the "residual

sector". See also RSU.

Assembly-language example to compute RESULT=56-3:

RESULT

# Allocate variable for output.

ARG1

DEC 56

ARG2 DEC

3

CLA ARG1

SUB

ARG2

STO RESULT

|

CLA

|

06

|

1

|

Store a value to the accumulator, from the memory word at

the address embedded within the instruction.

Recall that A1-A8 select the offset within a 256-word

sector, and A9 is the "residual bit" that selects between

the current sector and the "residual sector".

Assembly-langauge example to load the accumulator with

decimal 56:

K56

DEC

56

CLA K56

Note that as with the HOP

instruction, the assembler allows seemingly meaningless

usages like "CLA

LHS", where LHS

is the left-hand symbol of a code location rather that

the name of a variable or constant. What the

assembler does in this case is automatically, silently to

create a HOP constant in memory called "(LHS)",

and then to subsitute the "CLA

(LHS)" for the original instruction. See the

notes accompanying the HOP

instruction for full details.

|

AND

|

07

|

1

|

Logically ANDs the contents of the accumulator with the

contents of the address embedded within the instruction

and places the result in the accumulator. Recall

that A1-A8 select the offset within a 256-word sector,

and A9 is the "residual bit" that selects between the

current sector and the "residual sector".

Assembly-language example to compute RESULT=037&052

(i.e., to logically AND together octal 37 and octal

52):

RESULT

# Allocate variable for output.

ARG1 OCT

37

ARG2 OCT 52

CLA ARG1

SUB

ARG2

STO RESULT |

MPY

|

10

|

1

(results

available after 3)

| This is a

multiplication instruction. It multiplies two 24-bit

numbers to produce a 26-bit product. The accumulator

provides the address of one operand, and the address

embedded in the instruction points to the other

operand. Recall that A1-A8 select the offset within a

256-word sector, and A9 is the "residual bit" that selects

between the current sector and the "residual sector".

In both cases, the most-significant 24-bits of the operands

are used, and the least-significant 2 bits of the operand

are ignored. The result is available via the

SPQ

instruction on the 2nd instruction following MPY.

Any other instruction not involving multiplication or

division can be performed between the MPY

and the SPQ.

To illustrate the assembly-language syntax, let's multiply

the integer 56 by 3 and store the result in a variable:

RESULT

# Allocate variable for output.

K56

DEC 56

K3

DEC 3

CLA K56

MUL

K3 # Start the

multiplication.

NOP

# The result won't be available

NOP

# for a while, so kill some time.

SPQ

# Fetch product into accumulator.

STO RESULT # Save

it!

|

TRA

|

11

|

1

|

This is an unconditional jump instruction, which branches

to the address embedded in the instruction. Bits

A1-A9 of the embedded address represent the new offset

within either the currently-selected sector or the

residual sector. Note that the syllable remains the

same, so if (for example) the TRA is itself in syllable 1

of the current program counter, then the next instruction

executed will be at syllable 1 in the new program

counter. (This differs from the behavior of the

corresponding LVDC instruction, in

that the LVDC instruction allows selection of the target

syllable via A9, but does not allow the new program

counter to be in the residual sector.)

See also the description of shorthands

for various instructions.

Assembly-language examples:

# Branch

from location START to location FINISH.

START TRA

FINISH

...

FINISH

...

# Branch from location START2 to FINISH2, but use

# relative addressing rather than the left-hand

# symbol FINISH2. The NOP instructions below

# could be anything --- the point is simply that

# FINISH2 is 3 words in memory after START2.

START2 TRA *+3

NOP

NOP

FINISH2 ...

The operand for TRA

is either an existing left-hand symbol for an instruction

(rather than for a variable or constant), or else an

expression of the form "*+N" or "*-N", where N is any number from 1 to

7.

|

SHF

|

12

|

|

Performs a logical shift operation on the

accumulator. For this instruction, only bits A1-6

are actually used, as follows:

X

(A1-3)

|

Y

(A4-6)

|

Description of operation

|

|---|

1

|

2

| Shift "right" one

position

|

0

|

2

| Shift "right" two

positions |

X

|

3

| Shift "left" one

position |

X

|

4

| Shift "left" two

positions |

(Other)

| Clears the

accumulator

|

But what do "left" and "right" mean? Fortunately,

"left" implies multiplication by powers of two, and

"right" division by powers of two, just as modern

programmers are accustomed to.

For the left-shifts, 0 is shifted into the

least-significant bit at the right. For the

right-shifts, the sign-bit is duplicated into the

most-significant bit at the left.

For illegal X,Y combinations, the accumulator is

zeroed.

Note that this instruction is similar to the

corresponding LVDC instruction, but

differs in details.

See also the description of shorthands

for various instructions.

There assembly-language syntax for this instruction

is:

SHF

YX

(Or, you could just look at it as having a literal

octal constant as operand, and that constant was placed

directly into the bits A6-A1.) For example, to

shift right one position, X=1 and Y=2, so

SHF

21

|

TMI

|

13

|

1

|

This is a conditional jump instruction, which branches to

the address embedded in the instruction if the

accumulator is less than zero, but simply continues to

the next instruction in sequence if the accumulator

greater than or equal to zero. Bits A1-A9 of the

embedded address represent the new offset within the

currently selected 256-word instruction sector or the

residual sector. See also TNZ.

(This differs from the behavior of the corresponding

LVDC

instruction, in that the LVDC instruction allows

selection of the target syllable via A9, but does not

allow the new program counter to be in the residual

sector.)

Assembly-language examples:

# Branch

from location START to location FINISH

# because VALUE is negative:

VALUE DEC

-129

START TMI

FINISH

...

# Never gets here!

FINISH

...

# But does get to here!

# Don't branch from START2 to FINISH2, because

# VALUE2 is not negative:

VALUE2 DEC 127

START2 TMI

FINISH2

...

# Comes to here!

TRA BAILOUT

FINISH2

...

# Never comes to here!

BAILOUT ...

The operand for TMI

is either an existing left-hand symbol for an instruction

(rather than for a variable or constant), or else an

expression of the form "*+N" or "*-N", where N is any number from 1 to

7. The usage of the latter relative-addressing

forms isn't illustrated in the code example for

TMI,

but you can look at the code example for TRA

instead; it works exactly the same for TMI.

|

STO

|

14

|

1

|

Stores the contents of the accumulator in the word

indicated by the address embedded within the

instruction. Recall that A1-A8 select the offset

within a 256-word sector, and A9 is the "residual bit"

that selects between the current sector and the "residual

sector". The accumulator retains its

value.

Assembly-language example:

RESULT

# Allocate a variable

STO RESULT # Store

accumulator value in the variable.

Note that as with the HOP

instruction, the assembler allows seemingly meaningless

usages like "STO

LHS", where LHS

is the left-hand symbol of a code location rather that

the name of a variable or constant. What the

assembler does in this case is automatically, silently to

create a HOP constant in memory called "(LHS)",

and then to subsitute the "STO

(LHS)" for the original instruction. See the

notes accompanying the HOP

instruction for full details.

|

SPQ

|

15

|

1

| Store a product or

quotient (computed with MPY or

DIV)

into the word indicated by the address embedded within the

instruction. Recall that A1-A8 select the offset

within a 256-word sector, and A9 is the "residual bit" that

selects between the current sector and the "residual

sector". The accumulator retains its

value. (This instruction is somewhat similar to the

LVDC instruction

CLA

0775, though quite different in detail.)

For assembly-language examples, see MPY or

DIV

above.

|

CLD

|

16

|

1

|

A discrete input (i.e., a single bit) selected by the

operand address is read into the accumulator. The

entire accumulator is overwritten so that every bit

position has the value of the discrete input bit, and

consequently will be either 000000000 or else 377777777

octal. A test of either TMI

or TNZ

thereafter can thus branch on the basis of the bit

value.. A table of the

allowed discretes follows later. (This

instruction does not exist in the LVDC.)

See also the description of shorthands

for various instructions.

There assembly-language syntax for this instruction

is:

CLD

YX

(Or, you could just look at it as having a literal

octal constant as operand, and that constant was placed

directly into the bits A6-A1.) For example, to read

the MDIU data-ready bit, X=1 and Y=0, so

CLD

01 |

|

TNZ |

17

|

1

|

This is a conditional jump instruction, which branches to

the address embedded in the instruction if the

accumulator is not zero, but simply continues to the next

instruction in sequence if the accumulator is zero.

Bits A1-A8 of the embedded address represent the new word

address within the sector, while bit A9 selects between

the current sector vs. the residual sector. (In the

LVDC, A9 instead selects the syllable within the current

sector, which is possible since the LVDC has only 2

syllables.) See also TMI.

Assembly-language examples:

# Example

1: Branch to location IS129 if accumulator is

# equal to 129 and to ISNOT129 if accumulator is

not

# equal to 129:

K129 DEC

129

SUB K129

TNZ

ISNOT129

TRA IS129

...

IS129 ...

...

ISNOT129 ...

# Example 2: A simple loop with 10 iterations:

LOOPCTR

# Variable for counting loop iterations.

K1

DEC 1

K10

DEC 10

CLA

K10 # Setup for the

loop.

STO LOOPCTR

LOOP

...

# Do stuff

CLA LOOPCTR #

Decrement and test loop counter

SUB K1

TNZ LOOP

...

# Done!

The operand for TNZ

is either an existing left-hand symbol for an instruction

(rather than for a variable or constant), or else an

expression of the form "*+N" or "*-N", where N is any number from 1 to

7. The usage of the latter relative-addressing

forms isn't illustrated in the code example for

TNZ,

but you can look at the code example for TRA

instead; it works exactly the same for TNZ.

|

I/O Signals (For PRO

Instruction)

Note that in assembly language, in the

operand for a PRO

instruction, the Y operand field would proceed the X operand

field. So, for example, if X=3 and Y=4, the instruction

would be PRO43.

That's the opposite of present ordering of the columns in the

table below and could be confusing, for which I apologize, but

I'm too lazy to completely rewrite the table.

Operand

| Input /

Output

|

Signal

|

Comment

|

|---|

X

(A1-A3)

| Y

(A4-A6)

|

|---|

0

|

0

|

In

|

Digital Command System shift pulse gate

| Causes a 24-bit word

buffered in the Digital Command

System (DCS) to be read into bits M1-M24 of the

accumulator. Or, reads data from the Rendezvous Radar (if any).

|

0

|

1

|

Out

| Data

Transmission System control gate

| Used to output a data

word to the Instrumentation System

(IS) for digital downlink.

|

0

|

2

|

In/Out

| Time

Reference System data and timing pulses

| The action of this

signal seems pretty complex. Please read the section

on the Time Reference

System (TRS) for my conclusions as to what it's

actually supposed to do.

|

0

|

3

|

Out

| Digit

magnitude weight 1

|

Used in conjunction with "Digit magnitude weight 2",

"Digit magnitude weight 4", and "Digit magnitude weight

8" to write a particular digit to an MDR position previously

selected using the "Digit select weight X" outputs. The

weights derive from a BCD value of the digit whose

display is desired.

I haven't seen any explanation of how to clear a digit so

that it's blank ... perhaps there was no such feature,

though it seems to me that it would make data-entry very

confusing if so. There are a number of ways this

might have been done. Until I understand it better,

the yaPanel MDIU

emulator handles this as follows:

- Using any combination of magnitudes that doesn't

form a BCD (i.e., something in the range 0-9) will

clear the selected digit to be blank.

- Pressing the MDR's CLEAR button will make all of

the digits blank.

|

0

|

4

|

Out

| Reset

data ready, enter, and readout

| When zeroed, signals

the MDIU to reset

its internal buffer so that a numerical keystroke

subsequently be collected. It is unclear if this

needs to be returned to a non-zero state later. The

CLD

inputs associated with the ENTER and READ OUT keys also are

cleared as a result.

|

0

|

5

|

Out

| Digit

select weight 1

| Used in conjunction

with "Digit select weight 2" and "Digit select weight 4" to

select the next digit position to which a display value

will be output to the MDIU. It is not

really explained how these work, but I think that they are

used to form an index from 0-7 in the obvious way, and that

the leftmost address digit is 0, the 2nd address digit is

1, the leftmost message digit is 2, and so on. |

0

|

6

|

Out

|

Memory strobe

| I believe that this

signal is used only in conjunction with the

AGE for

testing purposes. When the accumulator is negative,

it seems to enable a hardware mode called "marginal early"

may help in determining how robust the memory access is

with respect to marginal timing. When the accumulator

is positive or zero, it disables this diagnostic

feature.

|

1

|

0

|

Out

|

Computer ready

| Signal to the Digital Command System (DCS) that the OBC

wishes to read a buffered uplinked data word. Also

used to tell the Rendezvous

Radar, if any, that radar data is required. In

the latter case, a 20 ms. delay must occur afterward before

polling the radar-ready discrete input (CLD00).

|

1

|

1

|

Out

| Drive

counters to zero

| For setting a delta-V

display on the IVI to zero. First

do PRO11

with the accumulator negative, then (see "Select X

counter") select the X, Y, or Z axis, then do PRO11

with the accumulator positive or zero to return to the

normal state. CLD31,

CLD25,

and CLD26

can be subsequently used for feedback that the displays are

actually at zero.

|

1

|

2

|

Out

|

Enter

| When inactive, the

Time Reference

System (TRS) is capable of receiving timing data (like

TR or

TX) from the ODC. When

active, the ODC can receive timing data (like ET or

TR) from the TRS. |

1

|

3

|

Out

| Digit

magnitude weight 2

| See Digit magnitude

weight 1

|

1

|

4

|

Out

|

Display device drive

|

The "display device drive", as far as I can see, is

what's used to turn the physical wheel on which the

MDIU

display-digits are inscribed to the proper position for

display. In other words when the drive is off

(i.e., PRO41 output a zero) the last-selected digit

continues to be displayed, while when the drive is on

(PRO41 output non-zero) the display wheel will be turned

if necessary. Therefore, the drive is normally off,

but is turned on briefly when a digit is being

changed. The full procedure is as follows:

- Use the digit-select weights to choose the

display-position which is supposed to be changed.

- Turn on the display device drive.

- Use the digit-magnitude weights to determine what

digit is driven into the selected display

position.

- Wait 0.5 seconds.

- Turn off the display device drive.

|

1

|

5

|

Out

| Digit

select weight 2

| See Digit select weight

1

|

1

|

6

|

|

Autopilot scale factor

|

|

2

|

0

|

Out

| Pitch

resolution

| Controls the range

switch for Pitch Error (or down range error) output.

If the sign bit is positive, then there is a 6-to-1

attenuation applied; if the sign bit is negative, there is

no attenuation.

|

2

|

1

|

Out

|

Select X counter

|

Used along with "Select Y counter" to select one of the

IVI's delta-V displays to receive

additional commands, as follows:

- X-axis: PRO12

with accumulator negative, PRO13

with accumulator positive or zero.

- Y-axis: PRO12

with accumulator positive or zero, PRO13

with accumulator negative.

- Z-axis: PRO12

with accumulator negative, PRO13

with accumulator negative.

|

2

|

2

|

Out

|

Aerospace Ground Equipment data link

| For outputting a single

data bit to the dedicated AGE data

link.

|

2

|

3

|

Out

| Digit

magnitude weight 4

| See Digit magnitude

weight 1 |

2

|

5

|

Out

| Digit

select weight 4

| See Digit select weight

1

|

2

|

6

|

In

| Reset

start computation

| From the PCDP's RESET switch.

|

3

|

0

|

Out

| Yaw

resolution

| Controls the range

switch for Yaw Error (or cross-range error) output.

If the sign bit is positive, then there is a 6-to-1

attenuation applied; if the sign bit is negative, there is

no attenuation. |

3

|

1

|

Out

|

Select Y counter

| See "Select X

counter".

|

3

|

2

|

Out

|

Aerospace Ground Equipment data clock

| Provides a data clock,

one pulse at a time, for reading data on the dedicated

AGE data

link.

|

3

|

3

|

Out

| Digit

magnitude weight 8

| See Digit magnitude

weight 1

|

3

|

4

|

In

| Read

Manual Data Insertion Unit insert data

| Reads a keystroke that

has been buffered in the MDIU. This operation

should be done only in response to a separate discrete

"Data ready" input via CLD.

The BCD value of the digit is stored into bits M1-M4 of the

accumulator. A PRO40

should be performed afterward to clear the MDIU buffer and

allow the next keystroke to be collected, and additional

PRO

instructions should be used to display the digit on the

MDIU.

|

3

|

6

|

Out

| Reset

radar ready

| Sent to the Rendezvous Radar, if any, to reset

its discrete input buffer.

|

4

|

0

|

Out

| Roll

resolution

| Controls the range

switch for Roll Error output. If the sign bit is

positive, then there is a 6-to-1 attenuation applied; if

the sign bit is negative, there is no attenuation. |

4

|

1

|

Out

|

Elapsed time control and Time Reference System control

reset / ATM wind-rewind reset

| Signal to the Time Reference System

(TRS) that the data about to be fetched from the TRS with

PRO20

commands is the elapsed time (ET). This output should

persist for 9-15 ms. before being returned to the normal

state. It also apparently acts to reset the TRS

control circuitry.

(Units with ATM

only.) It has additional functionality for the

Auxiliary Tape

Memory (ATM), in that it commands the ATM to stop

winding or rewinding. I believe that it also turns

off the ATM ERROR lamp. (I don't know how to select

between the TRS/ATM functions, or if it always performs

both simultaneously.)

|

4

|

3

|

Out

|

Computer malfunction

| To the PCDP's MALF light.

|

4

|

4

|

Out

| ATM

verify/repro command

| Send a command to the

Auxiliary Tape

Memory (ATM) to begin data output. I assume that

the accumulator is negative to begin the output and zero or

positive to end it.

|

4

|

6

|

TBD

|

Second stage engine cutoff

| TBD

|

5

|

0

|

Out

|

Computer running

| To the PCDP's COMP light.

|

5

|

1

|

In?/Out

| Time

to start re-entry calculations control / ATM wind

command

| The use for "time to

start re-entry calculations" is TBD.

(Units with ATM

only.) Initiates winding of the ATM. I

assume that the value in the accumulator should be

negative, however, I don't think that outputting a positive

or zero value stops the winding. Instead, use

PRO14. (I

don't know how to select between the timing and ATM

functions, or if it always performs both

simultaneously.) |

5

|

2

|

Out

| Time

to reset control / ATM rewind command

| Signal to the Time Reference System

(TRS) that transfer of time-to-equipment-reset

(TX) data is desired. This

output should persist for 9-15 ms. before being returned to

the normal state.

(Units with ATM

only.) Initiates rewinding of the ATM. I

assume that the value in the accumulator should be

negative, however, I don't think that outputting a positive

or zero value stops the rewinding. Instead, use

PRO14. (I

don't know how to select between the TRS/ATM functions, or

if it always performs both simultaneously.) |

5

|

3

|

Out

| Write

output processor

| For incrementally

adjusting the delta-V displays of the IVI. First, the X, Y, or Z display is

selected (see "Select X counter" above). No more than

1 ms. later, PRO35

is used to begin the update. The value in the

accumulator comprises the sign bit and M1-M12, so the

maximum change is -4096 to +4095. Since the displays

are actually -999 to +999, in theory the adjustment range

is more than full. In practice, only very small

adjustments would be made. My understanding of what

the hardware actually does is to increment or decrement the

displays by 1 every 21.5 ms., and that it will not be ready

to process another delta-V until the count has reached

zero. For example, trying to change the display by 25

would take about half a second, and no other outputs to the

IVI should take place in that interval. The "Velocity

error count not zero" discrete (CLD22)

can be polled to determine when the increment/decrement

pulses have all been sent to the display and the counter

has reached zero. |

5

|

4

|

In

| Read

delta velocity

|

This port is used to read the change in velocity from the

platform electronics, and to zero the reference velocity

for the next readings.

A single PRO45

instruction reads the ΔV from all three axes into

the accumulator. Documentation is unclear as to how

the data appearing in the accumulator is packed, but my

nearest guess as to what it's trying to tell us is that

each of the X, Y, and Z axis readings is a 4-bit

2's-complement value (thus being in the range -8 to +7),

and that they are packed into the accumulator as

follows:

XXXXYYYYZZZZ00000000000000

Even if correct, the units are TBD.

|

5

|

5

|

TBD

| Input

processor time

| TBD

|

5

|

6

|

Out

| Time

to retrofire control

| Signal to the Time Reference System

(TRS) that transfer of time-to-retrograde

(TR) data is desired. This

output should persist for 9-15 ms. before being returned to

the normal state. |

6

|

3

|

In

| Read

pitch gimbal

|

These ports are used for reading gimbal angles from the

inertial platform. The units used are TBD, as the

documents discussing them speak only of phase-shifted 400

cps voltages rather than true angles.

15-bit values are provided, including the sign bit and

the 14 most-significant bits. The 11

least-significant bits are zeroed. Each of the

PRO

commands associated with these ports both reads a

previously-measured value and begins accumulating a new

measurement, so these ports must be accessed in a very

specific procedure to get a complete set of readings, as

follows:

... at

least 5 ms. from last read of gimbals ...

PRO36 # Must ignore the first value

received.

... wait >= 5 ms. ...

PRO46

STO PITCH

... wait

>= 5 ms. ...

PRO56

STO ROLL

... wait

>= 5 ms. ...

PRO36

STO YAW

# The total time must be <=30 ms.

|

6

|

4

|

In

| Read

roll gimbal

|

6

|

5

|

In

| Read

yaw gimbal

|

7

|

0

|

Out

| Pitch

error command

| For the re-entry mode, the

outputs are down-range error rather than pitch error, and

cross-range error rather than yaw error.

These are values which are expected to be output at

intervals of 50 ms. or less, and feed into a 7-bit

digital-to-analog converter for driving the Flight Director

Indicator (FDI). The output comes from the

accumulator sign bit and from bit-positions M8-M13.

The analog outputs also feed into range switches which can

attenuate the signals, and are controlled by PRO02,

PRO03,

and PRO04.

|

7

|

1

|

Out

| Yaw

error command

|

7

|

2

|

Out

| Roll

error command

|

Discrete Inputs (For

CLD

Instruction)

Note that in assembly language, in the operand

for a CLD

instruction, the Y operand field would proceed the X operand

field. So, for example, if X=3 and Y=4, the instruction

would be CLD

43. That's the opposite of present ordering of the

columns in the table below and could be confusing, for which I

apologize, but as I said above, I'm too lazy to rewrite the

table.

Operand

|

Signal

|

Comment

|

|---|

X

(A1-A3)

| Y

(A4-A6)

|

|---|

0

|

0

| Radar

ready

| Indicates that data

from the Rendezvous Radar

(if any) is ready.

|

0

|

1

|

Computer mode 2

|

From the PCDP's COMPUTER mode

selector rotary dial. The rotary dial has 7

positions, encoded onto 3 discrete inputs, "Computer mode

1", "Computer mode 2", and Computer mode 3". The

encoding is:

Computer

Mode 1

|

Computer

Mode 2

|

Computer

Mode 3

|

Mode

|

|---|

0

|

0

|

0

|

TBD

|

0

|

0

|

1

|

Pre-launch

|

0

|

1

|

0

|

Ascent

|

0

|

1

|

1

|

Catch-up

|

1

|

0

|

0

|

Rendezvous

|

1

|

0

|

1

|

Re-entry

|

1

|

1

|

0

|

TBD

|

1

|

1

|

1

|

TBD

|

|

0

|

2

|

Spare

|

|

0

|

3

|

Processor timing phase 1

|

|

0

|

4

|

Spare

|

|

1

|

0

| Data

ready

| From the MDIU. It indicates

that a digit-keystroke has been buffered within the MDIU

and is ready to be read.

|

1

|

1

|

Computer mode 1

| See "Computer mode

2". |

1

|

2

| Start

computation

| From the PCDP's START switch

|

1

|

3

| X

zero indication

| Indicates that the

IVI's X-velocity display is at

zero.

|

1

|

4

| ATM

clock

| (Units with ATM only. Otherwise,

spare.) See the ATM section.

|

2

|

0

|

Enter

| From ENTER key of

MDIU

|

2

|

1

|

Instrumentation System sync

| From Instrumentation System (IS), to trigger

beginning of a new downlink cycle every 2.4

seconds.

|

2

|

2

|

Velocity error count not zero

| From the IVI. It is an indicator that a prior

"Write output processor" (PRO35)

has reached completion.

|

2

|

3

|

Aerospace Ground Equipment request

| From the AGE. Becomes

active (accumulator negative) when a word is available on

the dedicated AGE data link.

|

2

|

4

|

Spare

|

|

3

|

0

|

Readout

| From READ OUT key of

MDIU

|

3

|

1

|

Computer mode 3

| See "Computer mode

2". |

3

|

2

|

Spare

|

|

3

|

3

| ATM

on

| (Units with ATM only. Otherwise,

spare.) See the ATM

section. |

3

|

4

| ATM

data channel 2

| (Units with ATM only. Otherwise,

spare.) See the ATM

section. |

4

|

0

|

Clear

| From CLEAR key of

MDIU

|

4

|

1

| ATM

mode control 1

| (Units with ATM only. Otherwise,

spare.) See the ATM

section. |

4

|

2

|

Simulaton mode command

|

|

4

|

3

| ATM

end of tape

| (Units with ATM only. Otherwise,

spare.) See the ATM

section. |

4

|

4

| ATM

data channel 3

| (Units with ATM only. Otherwise,

spare.) See the ATM

section. |

5

|

0

| Time

to start re-entry calculations

| This is a signal from

the Time Reference

System (TRS) that its TR (time to

retrograde) counter has reached zero.

|

5

|

1

| ATM

mode control 2

| (Units with ATM only. Otherwise,

spare.) See the ATM

section. |

5

|

2

| Y

zero indication

| Indicates that the

IVI's Y-velocity display is

at zero. |

5

|

3

| ATM

data 1

| (Units with ATM only. Otherwise,

spare.) See the ATM

section. |

5

|

4

|

Spare

|

|

6

|

0

|

Digital Command System ready

| This is a signal from

the Digital Command System

(DCS)—i.e., the digital uplink from ground control—that

data is available for the OBC to read. In general, it

is expected that this signal be polled at 50 ms. intervals

or shorter. |

6

|

1

|

Fade-in discrete

| From the PCDP's FADE-IN. This is a signal from a

relay, but anything beyond that is TBD.

|

6

|

2

| Z

zero indication

| Indicates that the

IVI's Z-velocity display is

at zero. |

6

|

3

|

Umbilical disconnect

|

|

6

|

4

|

Spare

|

|

7

|

0

|

Instrumentation System request

|

|

7

|

1

| Abort

transfer

| From the PCDP's ABORT switch. The software should

poll it during ascent mode, and switch from ascent mode to

re-entry mode if the input becomes active.

|

7

|

2

|

Aerospace Ground Equipment input data

| Reads a single data bit

on the dedicated AGE data

link.

|

7

|

3

|

Spare

|

|

7

|

4

|

Spare

|

|

Subroutines

As weird as it may seem

in modern terms, the Gemini OBC

CPU had no mechanism for easily implementing

subroutines. Further, the assembly-language source

code for the OBC slavishly implemented what is basically a state

machine, using the separately designed "math flow" as a

pattern. Therefore the

OBC software developers had little need for

subroutines. You may think I'm wrong about this, but

I've pursued this question with several OBC developers to an